# DİZGİ EŞLEME ALGORİTMALARININ GPGPU HIZLANDIRICILARI KULLANILARAK ETKİLİ VE VERİMLİ HIZLANDIRILMASI

# EFFECTIVE AND EFFICIENT PARALLELIZATION OF STRING MATCHING ALGORITHMS USING GPGPU ACCELERATORS

Mengü NAZLI

Assist. Prof. Dr. Adnan ÖZSOY Supervisor

Submitted to Graduate School of Science and Engineering of Hacettepe University as a Partial Fulfillment to the Requirements for the Award of the Degree of Master of Science in Computer Engineering

# ÖZET

# DİZGİ EŞLEME ALGORİTMALARININ GPGPU HIZLANDIRICILARI KULLANILARAK ETKİLİ VE VERİMLİ HIZLANDIRILMASI

Mengü NAZLI

# Yüksek Lisans, Bilgisayar Mühendisliği Danışman: Dr. Öğretim Üyesi Adnan ÖZSOY Haziran 2020, 117 sayfa

Dizgi eşleme, bilgisayar bilimlerinin en eski ve üzerinde en çok çalışılan konularından biridir. Bilgisayar güvenliği, biyoinformatik, sosyal medya işleme, veri madenciliği, veri sıkıştırma, kodlama teorisi ve benzeri pek çok alanda dizgi işleme uygulamalarına rastlanmaktadır. 1970'lerden bu yana dizgi eşleme problemi üzerine pek çok farklı performans karakteristiğine ve çalışma şekline sahip algoritma önerilmiştir. Bu alandaki çalışmaların çeşitliliği, kapsamlı bir karşılaştırmanın hazırlanmasını zor kılsa da, Thierry Lecroq ve Simone Faro tarafından geliştirilen SMART kütüphanesi gibi bu hedefe ulaşmış birkaç çalışmaya rastlanmaktadır. Bu kütüphane, dizgi işleme alanında çalışmak, literatürdeki algoritmaları karşılaştırmak ve yeni algoritmalar geliştirip mevcut algoritmalarla kıyaslamak isteyen araştırmacılar için değerli bir kaynaktır. Ancak kütüphanedeki kodların seri olarak çalışacak şekilde geliştirilmiş olması, içinde bulunduğumuz yüksek performanslı paralel hesaplama çağında bu kütüphanenin uygulamadaki pratikliğini azaltmaktadır. Bu çalışmada, benzer bir kütüphaneyi Nvidia tarafından geliştirilen CUDA platformundan yararlanarak paralel bir şekilde hazırladık ve dizgi eşleme algoritmalarının paralel çalışma performanslarını incelemeyi amaçladık. CUSMART adı verdiğimiz kütüphanede CUDA C++ programlama arayüzünü kullanarak 85'den fazla dizgi eşleme algoritmasının paralel ortama aktardık ve bu algoritmaları farklı senaryolarda test ederek algoritmaların güçlü ve zayıf yanlarını adil bir şekilde karşılaştırabilmeyi hedefledik. Hazırladığımız algoritmaları hem Nvidia tarafından geliştirilen mobil platform Jetson'da, hem de genel kullanım için piyasaya sürülmüş olan GeForce serisi kartlarda test ettik. Elde ettiğimiz sonuçlar, aynı algoritmaların seri CPU versiyonlarına göre ortalama 40 kat daha hızlı çalıştığını göstermekte ve GPGPU platformunun dizli işleme uygulamalarındaki potansiyeline işaret etmektedir.

Anahtar Kelimeler: dizgi eşleme, paralel programlama, GPU programlama, GPGPU, NVIDIA, CUDA, CUSMART

# ABSTRACT

# EFFECTIVE AND EFFICIENT PARALLELIZATION OF STRING MATCHING ALGORITHMS USING GPGPU ACCELERATORS

# Mengü NAZLI

# Master of Science, Department of Computer Engineering Supervisor: Assist. Prof. Dr. Adnan ÖZSOY June 2020, 117 pages

String matching is one of the oldest and actively studied problems in computer science. It has applications in computer security, bio-informatics, social media processing, data mining, data compression, coding theory, and many other areas. Since the '70s, there have been dozens of proposed algorithms to this problem with different approaches and performance characteristics. While the sheer amount of proposed algorithms makes it hard to put together a comprehensive performance comparison study, there are a few projects like the String Matching Algorithms Research Tool (SMART) library from Thierry Lecroq and Simone Faro achieving this goal. Their library holds the code implementations for the majority of string matching algorithms in the literature. It is an invaluable tool for studying different string matching algorithms, but it lacks practicality because of its serial implementation in the age of parallel computation. Our aim is to present a parallel version of the library realized on the CUDA platform by Nvidia, employing GPGPU programming concepts for improved performance and gain insight on the parallel versions of these algorithms. We have developed CUSMART library, which contains parallelized versions of around 85 string matching algorithms using CUDA API. The performances of these algorithms are tested with different scenarios to get a fair comparison and determine their strong/weak application scenarios. Also, we have investigated some well-known optimization practices to observe how they impact the performance of these algorithms. Our results show an average of 40x speedup compared to the serial CPU version of algorithms indicating the potential of GPGPU computing on string matching applications.

**Keywords:** string matching, parallel programming, GPU programming, GPGPU, NVIDIA, CUDA, CUSMART

# ACKNOWLEDGEMENTS

I would like to express my gratitude to my supervisor Assist. Prof. Dr. Adnan Özsoy for introducing me to the topic of general-purpose GPU computing and providing support. His helpful comments, remarks, and engagement through the learning process of this master thesis were invaluable to me. He continuously allocated a portion of his valuable time for consultation throughout this work despite his busy schedule.

I also had great pleasure working with Onur Cankur and Behzad Naderalvojoud and appreciate their collaboration on the project which this thesis stemmed from. This thesis would not be complete without their contribution and countless hours of work.

I would like to acknowledge the support of The Scientific and Technological Research Council of Turkey (TÜBİTAK) with grant number 117E142. We have obtained the hardware required to conduct the research, thanks to their funding support.

Particularly helpful to me during the final days of my thesis preparation was Koray Tarakçı, who aided me in finishing the required paperwork. I am indebted to him for his invaluable assistance under difficult circumstances of the pandemic crisis in a quarantined city.

Finally, I must express my very profound gratitude to my parents and to my friends for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis. This accomplishment would not have been possible without them. Thank you. "People think that computer science is the art of geniuses but the actual reality is the opposite, just many people doing things that build on each other, like a wall of mini stones."

Donald Knuth

# CONTENTS

| ÖZET               |                                                     | <br>• | i    |

|--------------------|-----------------------------------------------------|-------|------|

| ABSTRACT           |                                                     | <br>• | iii  |

| ACKNOWLEDGEN       | MENTS                                               | <br>• | v    |

| CONTENTS           |                                                     | <br>• | xi   |

| LIST OF FIGURES    | 8                                                   | <br>• | xiii |

| LIST OF TABLES     |                                                     | <br>• | XV   |

| 1 INTRODUCTION     | N                                                   | <br>• | 1    |

| 2 BACKGROUND       |                                                     | <br>• | 4    |

| 2.1 String Matchin | ng                                                  | <br>• | 4    |

| 2.1.1 Compari      | son Based Algorithms                                | <br>• | 5    |

| 2.1.1.1            | Brute Force (BF) - N/A                              | <br>• | 5    |

| 2.1.1.2            | Morris-Pratt (MP) - 1970                            | <br>• | 6    |

| 2.1.1.3            | Knuth-Morris-Pratt (KMP) - 1977                     | <br>• | 6    |

| 2.1.1.4            | Boyer-Moore (BM) - 1977                             | <br>• | 6    |

| 2.1.1.5            | Horspool (HOR) - 1980                               | <br>• | 7    |

| 2.1.1.6            | Galil-Seiferas (GS) - 1981                          | <br>• | 7    |

| 2.1.1.7            | Apostolico-Giancarlo (AG) - 1986                    | <br>• | 7    |

| 2.1.1.8            | Karp-Rabin (KR) - 1987                              | <br>• | 7    |

| 2.1.1.9            | Zhu-Takaoka (ZT) - 1987                             | <br>• | 8    |

| 2.1.1.10           | Quick Search (QS) - 1990                            | <br>• | 8    |

| 2.1.1.11           | Optimal Mismatch (OM) - 1990                        | <br>• | 8    |

| 2.1.1.12           | Maximal Shift (MS) - 1990                           | <br>• | 8    |

| 2.1.1.13           | Apostolico-Crochemore (AC) - 1991                   | <br>• | 8    |

| 2.1.1.14           | Two Way (TW) - 1991                                 | <br>• | 9    |

| 2.1.1.15           | Tuned Boyer-Moore (TUNBM) - 1991                    | <br>• | 9    |

| 2.1.1.16           | Colussi (COL) - 1991                                |       | 9    |

| 2.1.1.17           | Smith (SMITH) - 1990                                | <br>• | 9    |

| 2.1.1.18           | Galil-Giancarlo (GG) - 1992                         |       | 9    |

| 2.1.1.19           | Raita (RAITA) - 1992                                |       | 9    |

| 2.1.1.20           | String Matching on Ordered Alphabet (SMOA) - 1992 . |       | 10   |

| 2.1.1.21           | Turbo Boyer-Moore (TBM) - 1992                      | <br>• | 10   |

| 2.1.1.22           | Not So Naive (NSN) - 1993                           |       | 10   |

| 2.1.1.23           | Reverse Colussi (RCOL) - 1994                       |       | 10   |

| 2.1.1.24           | Skip Search (SKIP) - 1998                           |       | 10   |

| 2.1.1.25           | Alpha Skip Search (ASKIP) - 1998                    |       | 11   |

| 2.1.1.2       | 6 Knuth-Morris-Pratt Skip Search (KMPS) - 1998             | 11 |

|---------------|------------------------------------------------------------|----|

| 2.1.1.2       | 7 Berry-Ravindran (BR) - 1999                              | 11 |

| 2.1.1.2       | 8 Ahmed-Kaykobad-Chowdhury (AKC) - 2003                    | 11 |

| 2.1.1.2       | 9 Fast Search (FS) - 2003                                  | 11 |

| 2.1.1.3       | 0 Forward Fast Search (FFS) - 2004                         | 11 |

| 2.1.1.3       | 1 Backwards Fast Search (BFS) - 2004                       | 11 |

| 2.1.1.3       | 2 Tailed Substring (TS) - 2004                             | 12 |

| 2.1.1.3       | 3 Sheik-Sumit-Anindya-Balakrishnan-Sekar (SSABS) - 2004 .  | 12 |

| 2.1.1.3       | 4 Thathoo-Virmani-Sai-Balakrishan-Sekar (TVSBS) - 2006.    | 12 |

| 2.1.1.3       | 5 Boyer-Moore-Horspool using Probabilities (PBMH) - 2006 . | 12 |

| 2.1.1.3       | 6 Franek-Jennings-Smyth (FJS) - 2007                       | 12 |

| 2.1.1.3       | 7 Wu-Manber for Single Pattern Matching (HASHQ) - 2007 .   | 12 |

| 2.1.1.3       | 8 Boyer-Moore-Horspool with q-grams (BMHQ) - 2008          | 12 |

| 2.1.1.3       | 9 Two Sliding Windows (TSW) - 2008                         | 13 |

| 2.1.2 Autom   | ata based algorithms                                       | 13 |

| 2.1.2.1       | Deterministic Finite Automata (DFA) - N/A                  | 13 |

| 2.1.2.2       | Reverse Factor (RF) - 1992                                 | 14 |

| 2.1.2.3       | Simon (SIM) - 1994                                         | 14 |

| 2.1.2.4       | Turbo Reverse Factor (TRF) - 1994                          | 14 |

| 2.1.2.5       | Forward DAWG Matching (FDM) - 1994                         | 14 |

| 2.1.2.6       | Backward DAWG Matching (BDM) - 1994                        | 14 |

| 2.1.2.7       | Backward Oracle Matching (BOM) - 1999                      | 14 |

| 2.1.2.8       | Double Forward DAWG Matching (DFDM) - 2000                 | 15 |

| 2.1.2.9       | Wide Window (WW) - 2005                                    | 15 |

| 2.1.2.1       | 0 Linear DAWG Matching (LDM) - 2005                        | 15 |

| 2.1.2.1       | 1 Improved Linear DAWG Matching (ILDM) - 2006              | 15 |

| 2.1.2.1       | 2 Extended Backward Oracle Matching (EBOM) - 2008          | 15 |

| 2.1.2.1       | 3 Forward Backward Oracle Matching (FBOM) - 2008           | 16 |

| 2.1.2.1       | 4 Simplified Extended Backward Oracle Matching (SEBOM) -   |    |

|               | 2009                                                       | 16 |

| 2.1.2.1       | 5 Simplified Forward Backward Oracle Matching (SFBOM) -    |    |

|               | 2009                                                       | 16 |

| 2.1.2.1       | 6 Backward SNR DAWG Matching (BSDM) - 2012                 | 16 |

| 2.1.3 Bit-Par | allel Based Algorithms                                     | 16 |

| 2.1.3.1       | Shift-Or (SO) - 1989                                       | 17 |

| 2.1.3.2       | Shift-And (SA) - 1989                                      | 17 |

| 2.1.3.3       | Backward Nondeterministic DAWG Matching (BNDM) - 1998      | 17 |

| 2.1.3.4       | Backward Nondeterministic DAWG Matching for Long Patterns  |    |

|               | (LBNDM) - 2000                                             | 17 |

| 2.1.3.5          | Simplified Backward Nondeterministic DAWG Matching (SB-  |    |

|------------------|----------------------------------------------------------|----|

|                  | NDM) - 2003                                              | 17 |

| 2.1.3.6          | Two-Way Nondeterministic DAWG Matching (TNDM) - 2003     | 17 |

| 2.1.3.7          | Shift Vector Matching (SVM) - 2003                       | 18 |

| 2.1.3.8          | BNDM with loop unrolling (BNDM2) - 2005                  | 18 |

| 2.1.3.9          | Simplified BNDM with loop unrolling (SBNDM2) - 2005      | 18 |

| 2.1.3.10         | BNDM with Boyer-Moore-Horspool Shift (BNDMBMH) - 2005    |    |

|                  |                                                          | 18 |

| 2.1.3.1          | Horspool with BNDM test (BMHBNDM) - 2005                 | 18 |

| 2.1.3.12         | 2 Forward Nondeterministic DAWG Matching (FNDM) - 2005   | 18 |

| 2.1.3.13         | Bit Parallel Wide Window (BWW) - 2005                    | 18 |

| 2.1.3.14         | 4 Average Optimal Shift-Or (AOSO) - 2005                 | 19 |

| 2.1.3.15         | 5 Fast Average Optimal Shift-Or (FAOSO) - 2005           | 19 |

| 2.1.3.10         | 6 Forward BNDM (FBNDM) - 2008                            | 19 |

| 2.1.3.17         | 7 Forward Simplified BNDM (FSBNDM) - 2008                | 19 |

| 2.1.3.18         | 8 Bit-Parallel Length Invariant Matcher (BLIM) - 2008    | 19 |

| 2.1.3.19         | Backwards Nondeterministic DAWG Matching with q-grams    |    |

|                  | (BNDMQ) - 2009                                           | 19 |

| 2.1.3.20         | O Simplified BNDM with q-grams (SBNDMQ) - 2009           | 19 |

| 2.1.3.2          | I Forward Nondeterministic DAWG Matching with q-grams -  |    |

|                  | 2009                                                     | 20 |

| 2.1.3.22         | 2 Small Alphabet Bit-Parallel (SABP) - 2009              | 20 |

| 2.1.3.23         | 3 Backwards Nondeterministic DAWG Matching with Extended |    |

|                  | shifts (BXS) - 2010                                      | 20 |

| 2.1.3.24         | 4 Factorized BNDM (KBNDM) - 2010                         | 20 |

| 2.2 General-purp | oose Computing on Graphics Processing Unit with CUDA     | 21 |

| 2.2.1 Heterog    | geneous Architecture                                     | 25 |

| 2.2.2 Paradig    | m of Heterogeneous Computing                             | 27 |

| 2.2.3 CUDA:      | A Platform for Heterogeneous Computing                   | 27 |

| 2.2.4 CUDA       | Programming Model                                        | 29 |

| 2.2.5 Managi     | ng Memory                                                | 31 |

|                  | zing Threads                                             | 32 |

|                  | Execution                                                | 33 |

|                  | Execution Model                                          | 34 |

| 2.2.8.1          | Warp Divergence                                          | 36 |

| 2.2.8.2          | Resource Partitioning                                    | 37 |

| 2.2.8.3          | Occupancy                                                | 38 |

| 2.2.8.4          |                                                          | 38 |

|       | 2.2.9 Memory Model                                    | • | • |   | • | • | • | • | • | 39 |

|-------|-------------------------------------------------------|---|---|---|---|---|---|---|---|----|

|       | 2.2.9.1 Registers                                     | • | • |   | • | • | • |   |   | 40 |

|       | 2.2.9.2 Global Memory                                 | • | • | • | • | • | • |   | • | 42 |

|       | 2.2.9.3 Shared Memory                                 | • | • |   | • |   |   |   |   | 42 |

|       | 2.2.9.4 Constant Memory                               | • | • |   | • | • | • |   |   | 43 |

|       | 2.2.9.5 Texture Memory                                | • | • |   | • | • | • | • |   | 43 |

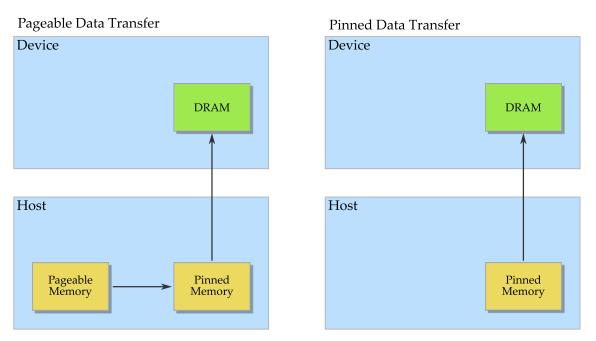

|       | 2.2.9.6 Pinned Memory                                 | • | • | • | • |   | • |   | • | 44 |

| 3 REI | LATED WORK                                            | • | • | • | • | • | • |   | • | 46 |

| 4 CUS | SMART                                                 | • | • |   | • |   |   |   |   | 52 |

| 4.1   | Main Structure of the Library                         | • | • |   | • |   |   |   |   | 54 |

|       | 4.1.1 Applied parallelization techniques              | • | • |   | • |   |   |   |   | 55 |

|       | 4.1.2 Granularity of Parallelism                      | • | • | • | • | • | • |   | • | 56 |

|       | 4.1.3 Streaming Operation                             | • | • |   | • | • | • | • |   | 56 |

|       | 4.1.4 Shared and Constant Memory                      | • | • |   | • | • | • | • |   | 57 |

|       | 4.1.5 Pinned Memory                                   | • | • | • | • | • | • |   | • | 58 |

|       | 4.1.6 Occupancy                                       | • | • | • | • |   | • |   | • | 58 |

|       | 4.1.7 Algorithm Testing                               | • | • |   | • |   |   |   |   | 58 |

|       | 4.1.7.1 Preprocessing Steps                           | • | • |   | • | • | • | • |   | 58 |

|       | 4.1.7.2 Timing of the Search Operations               | • | • |   | • | • |   | • |   | 59 |

|       | 4.1.7.3 Fair Comparison                               | • | • |   | • |   |   |   |   | 59 |

|       | 4.1.7.4 Computation of the Total Match Count          | • | • | • | • |   |   |   |   | 60 |

|       | 4.1.8 Introducing New Algorithms to the Library       | • | • | • | • | • | • |   | • | 61 |

| 5 EXI | PERIMENTS AND RESULTS                                 | • | • | • | • | • | • |   | • | 62 |

| 5.1   | Testing Equipment                                     | • | • |   | • |   |   |   |   | 62 |

|       | 5.1.1 Workstation Specifications                      | • | • | • | • | • | • |   | • | 62 |

|       | 5.1.2 Mobile System Specifications                    | • | • |   | • | • |   | • |   | 62 |

| 5.2   | Test Cases                                            | • | • |   | • | • | • | • |   | 63 |

|       | 5.2.1 Structured Text Datasets                        | • | • |   | • |   |   |   |   | 63 |

|       | 5.2.2 Genome Datasets                                 | • | • |   | • | • | • | • |   | 63 |

|       | 5.2.3 Syntetic Repeating Datasets                     | • | • |   | • | • | • | • |   | 64 |

|       | 5.2.4 Syntetic Randomized Datasets                    | • | • |   | • | • | • |   |   | 64 |

| 5.3   | Results                                               | • | • |   | • | • | • | • |   | 64 |

|       | 5.3.1 Optimal Search String Length                    | • | • |   | • | • | • | • |   | 64 |

|       | 5.3.2 The Parallel Algorithm Performance Rankings.    | • | • |   | • |   |   |   |   | 66 |

|       | 5.3.3 Genome Data Test Results                        |   | • |   | • |   |   |   |   | 68 |

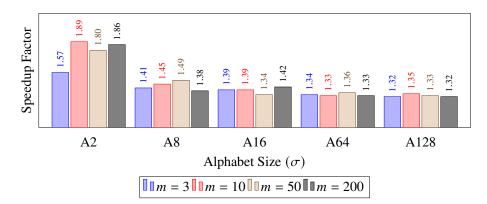

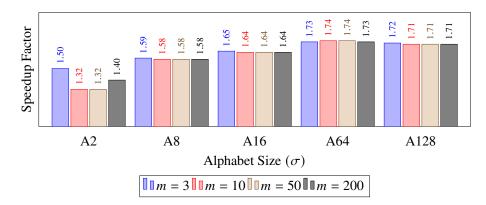

|       | 5.3.4 Different Alphabet Test Results                 | • | • |   | • |   |   |   |   | 70 |

|       | 5.3.5 Mobile unit tests performed on Nvidia Jetson TX | 2 | • | • | • | • |   | • |   | 76 |

|       | 5.3.6 The Parallelism Granularity Test Results        | • | • |   | • | • |   |   |   | 78 |

|       | 5.3.7 Constant Memory Test Results                    |   | • |   | • |   |   |   |   | 79 |

|       |                                                       |   |   |   |   |   |   |   |   |    |

| 5.3.8 Shared Memory Test Results | • | <br>79 |

|----------------------------------|---|--------|

| 5.3.9 Overlapping Test Results   | • | <br>83 |

| 6 CONCLUSION                     | • | <br>85 |

| BIBLIOGRAPHY                     | • | <br>87 |

# LIST OF FIGURES

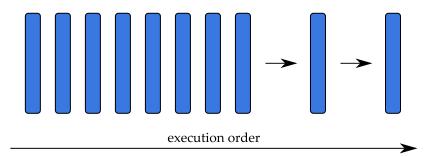

| Serial execution of work partitions in order.                                | 21                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

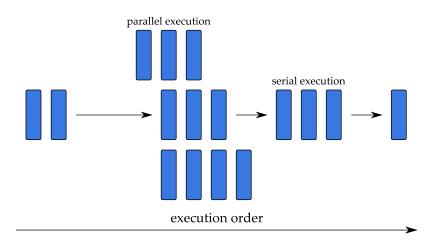

| Execution of work partitions in serial and parallel order                    | 22                                                                                                                                                                                                                            |

| Different types of partitioning. Top row shows the entire data, second row   |                                                                                                                                                                                                                               |

| is block partitioned configuration and the third row is cyclic partitioned   |                                                                                                                                                                                                                               |

| configuration                                                                | 23                                                                                                                                                                                                                            |

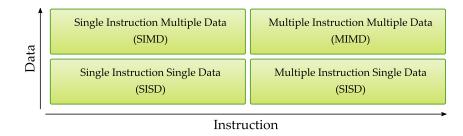

| Different types of instruction and data level parallelism configurations.    |                                                                                                                                                                                                                               |

| (Source: [72])                                                               | 23                                                                                                                                                                                                                            |

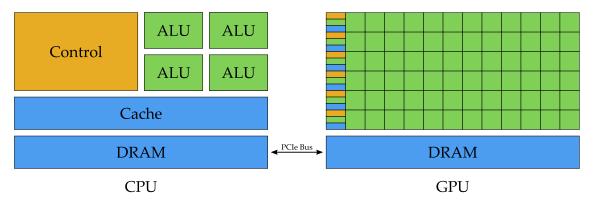

| Communication between CPU and GPU. (Source: [72])                            | 26                                                                                                                                                                                                                            |

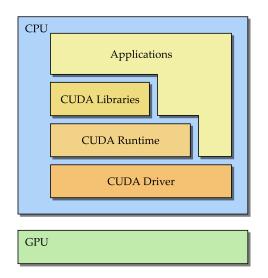

| CUDA application layers (Source: [72])                                       | 28                                                                                                                                                                                                                            |

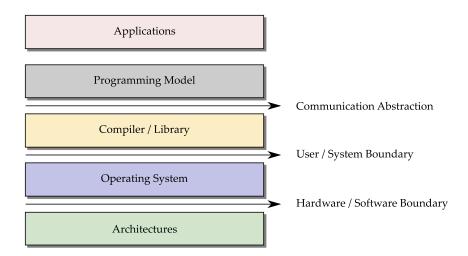

| CUDA programming abstraction layers. (Source: [72])                          | 29                                                                                                                                                                                                                            |

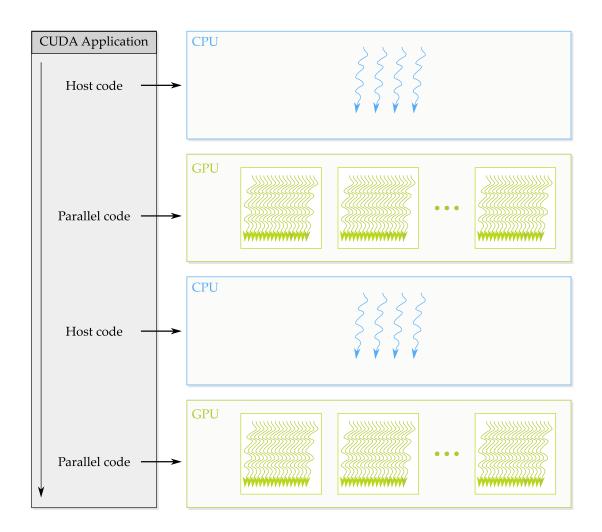

| CUDA application program flow. (Source: [72])                                | 30                                                                                                                                                                                                                            |

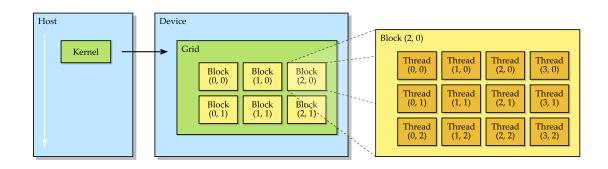

| CUDA Kernel call and thread hierarchy. (Source: [72])                        | 32                                                                                                                                                                                                                            |

| An example kernel configuration with thread indexes. (Source: [72])          | 34                                                                                                                                                                                                                            |

| Warp divergence caused by an if-else clause and resulting thread stall.      |                                                                                                                                                                                                                               |

| (Source: [72])                                                               | 37                                                                                                                                                                                                                            |

| CUDA memory hierarchy. (Source: [72])                                        | 40                                                                                                                                                                                                                            |

| CUDA device memory diagram. (Source: [72])                                   | 41                                                                                                                                                                                                                            |

| Allocating pinned memory using CUDA directives. (Source: [72])               | 44                                                                                                                                                                                                                            |

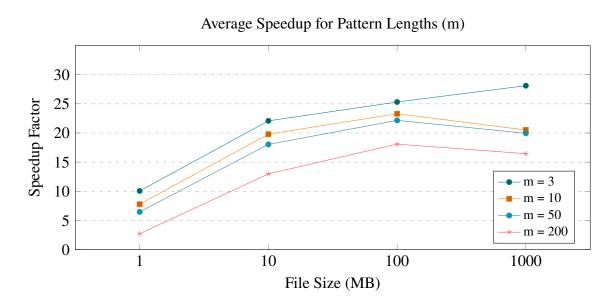

| The average speed-up of parallel algorithms with regards to various pattern  |                                                                                                                                                                                                                               |

| lengths over various text lengths                                            | 65                                                                                                                                                                                                                            |

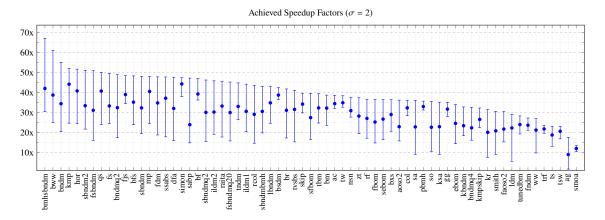

| The obtained speedup factors for 2 character alphabet, ordered from high-    |                                                                                                                                                                                                                               |

| est to lowest. Vertical lines represent the range of speedup factors the     |                                                                                                                                                                                                                               |

| algorithm achieves with the tested set of patterns                           | 72                                                                                                                                                                                                                            |

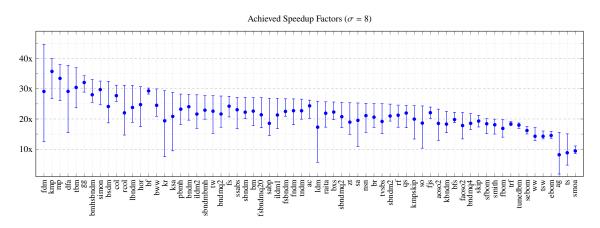

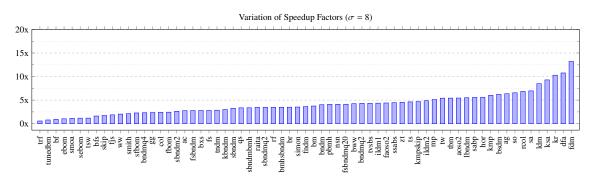

| The obtained speedup factors for 8 character alphabet, ordered from high-    |                                                                                                                                                                                                                               |

| est to lowest. Vertical lines represent the range of speedup factors the     |                                                                                                                                                                                                                               |

| algorithm achieves with the tested set of patterns                           | 72                                                                                                                                                                                                                            |

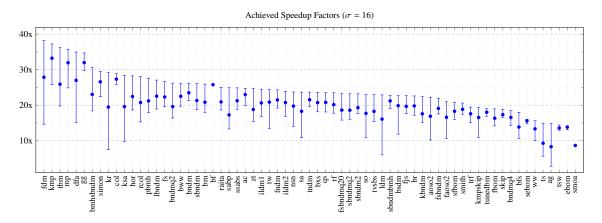

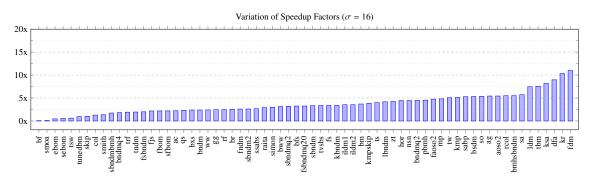

| The obtained speedup factors for 16 character alphabet, ordered from         |                                                                                                                                                                                                                               |

| highest to lowest. Vertical lines represent the range of speedup factors the |                                                                                                                                                                                                                               |

| algorithm achieves with the tested set of patterns                           | 73                                                                                                                                                                                                                            |

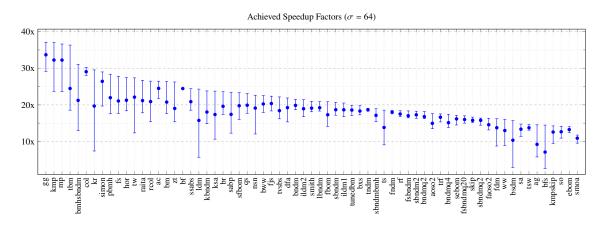

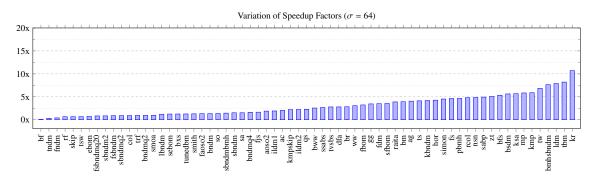

| The obtained speedup factors for 64 character alphabet, ordered from         |                                                                                                                                                                                                                               |

| highest to lowest. Vertical lines represent the range of speedup factors the |                                                                                                                                                                                                                               |

| algorithm achieves with the tested set of patterns                           | 73                                                                                                                                                                                                                            |

|                                                                              | Execution of work partitions in serial and parallel order Different types of partitioning. Top row shows the entire data, second row is block partitioned configuration and the third row is cyclic partitioned configuration |

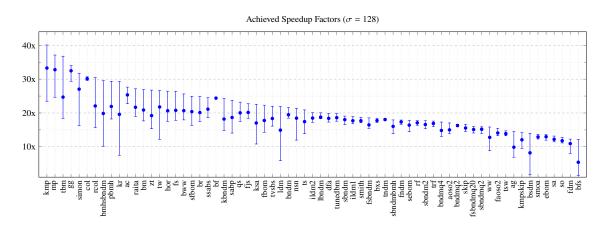

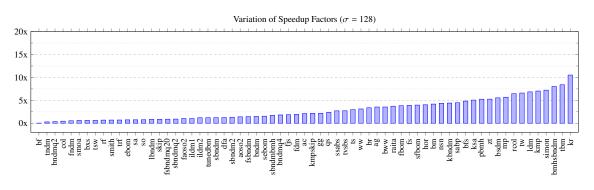

| 5.6  | The obtained speedup factors for 128 character alphabet, ordered from           |    |

|------|---------------------------------------------------------------------------------|----|

|      | highest to lowest. Vertical lines represent the range of speedup factors the    |    |

|      | algorithm achieves with the tested set of patterns                              | 73 |

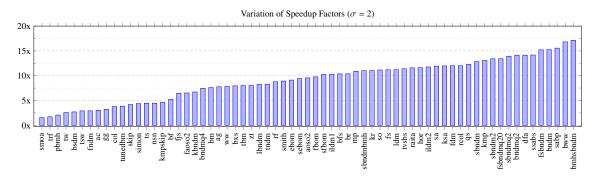

| 5.7  | The variation values of algorithm speedups for alphabet size $\sigma = 2$       | 74 |

| 5.8  | The variation values of algorithm speedups for alphabet size $\sigma = 8$       | 74 |

| 5.9  | The variation values of algorithm speedups for alphabet size $\sigma$ = 12 $$ . | 75 |

| 5.10 | The variation values of algorithm speedups for alphabet size $\sigma = 64$      | 75 |

| 5.11 | The variation values of algorithm speedups for alphabet size $\sigma = 128$ .   | 75 |

| 5.12 | Speed-up factors of overlapping for different alphabet and pattern sizes,       |    |

|      | without pinned memory usage                                                     | 83 |

| 5.13 | Speed-up factors of overlapping for different alphabet and pattern sizes,       |    |

|      | with pinned memory usage                                                        | 84 |

# LIST OF TABLES

| 2.1  | Microarchitectures introduced by Nvidia over years                                  | 27 |

|------|-------------------------------------------------------------------------------------|----|

| 2.2  | Memory manipulation functions for host and device                                   | 31 |

| 2.3  | Feature summary of CUDA device memory types                                         | 43 |

| 5.1  | The average speed-ups of parallel algorithms with regards to various pat-           |    |

|      | tern lengths over various structured text lengths                                   | 65 |

| 5.2  | Top 5 parallel string matching algorithms for each pattern length $(m)$ over        |    |

|      | 100MB wikipedia text                                                                | 66 |

| 5.3  | Bottom 5 parallel string matching algorithms for each pattern length ( <i>m</i> )   |    |

|      | over 100MB wikipedia text                                                           | 68 |

| 5.4  | Most stable 5 parallel string matching algorithms for each pattern length           |    |

|      | (m) over 100MB wikipedia text                                                       | 68 |

| 5.5  | Top 5 parallel string matching algorithms for each pattern $length(m)$ over         |    |

|      | 100MB DNA sequence                                                                  | 69 |

| 5.6  | Bottom 5 parallel string matching algorithms for each patternlength $(m)$           |    |

|      | over 100MB DNA sequence                                                             | 69 |

| 5.7  | Most stable 5 parallel string matching algorithms for each pattern length           |    |

|      | ( <i>m</i> ) over 100MB DNA sequence                                                | 70 |

| 5.8  | The Runtime of top 5 algorithms for different alphabet sizes ( $\sigma$ ), times    |    |

|      | are the average values of 4 different pattern tests                                 | 71 |

| 5.9  | The Runtime of bottom 5 algorithms for different alphabet sizes ( $\sigma$ ), times |    |

|      | are the average values of 4 different pattern tests                                 | 71 |

| 5.10 | The specifications of the hardware tested.                                          | 76 |

| 5.11 | Jetson TX2 top 5 parallel string matching algorithms for each pattern               |    |

|      | length (m) over 100MB wikipedia text.                                               | 77 |

| 5.12 | Jetson TX2 bottom 5 parallel string matching algorithms for each pattern            |    |

|      | length (m) over 100MB wikipedia text.                                               | 77 |

| 5.13 | Jetson TX2 most stable 5 parallel string matching algorithms for each               |    |

|      | pattern length (m) over 100MB wikipedia text                                        | 77 |

| 5.14 | The algorithm runtimes (ms) for different stride length factors                     | 80 |

| 5.15 | Average speed factors with constant memory usage compared to global                 |    |

|      | memory. Tested on 100 MB DNA dataset.                                               | 81 |

| 5.16 | Top 5 algorithms with improved performance when constant memory is                  |    |

|      | used                                                                                | 81 |

| 5.17 | Comparison of total search operation times based on the memory type.   |    |

|------|------------------------------------------------------------------------|----|

|      | Preprocessed data is stored on global and shared memory for these test |    |

|      | cases                                                                  | 82 |

# **1. INTRODUCTION**

String matching is an important subject in the text processing field. It is an essential component used by the functioning software on many operating systems. The programming methods emphasized by string matching serve as paradigms in other fields of computer science. Although data are shared and stored in many forms, the text remains as the dominant form of information handling. This is especially apparent in literature where data are composed of large corpora. Similarly, computer science is also a case where massive amounts of data are stored in linear data files. Molecular biology is another example where biological molecules are approximated as the sequence of more fundamental building blocks like amino acids or nucleotides handled as strings. String matching solutions are applied in many other areas such as computer security [1], bio-informatics [2], [3], social media content processing [4], data mining [5], data compression [6], coding theory [7], [8] and forms the basis of these areas.

Data usage and collected data are increasing day by day in these computer-centric areas. The processing and calculation requirements of this incremental data are also on the same scale. It requires new solutions and hardware support to meet the increase. This problem, which is of interest to high-performance computations and Big data, has gained more importance in recent years. The increase in the calculation time due to the increase in data corresponds to very prolonged response times in many applications, which results in slow and unacceptable runtimes. Therefore, it is important to reduce the calculation times for the availability of the systems.

Parallel processing to reduce calculation times is the primary solution approach for highperformance calculations. The Central Processing Unit (CPU) was the leading architecture for many years on which parallel calculations are based on [9]. With the increasing number of processors used in the systems, calculations in the applications are distributed to the multi-system supercomputers and the multi-core processors in each system. The physical boundaries of multi-core processors such as heat and power usage limit the increase in the number of cores in today's CPUs [10], [11]. In order to overcome these limitations, researches using hardware other than the CPU for high-performance computations have an important place in the literature [12], [13]. One of these types of equipment is the Graphics Processing Unit (GPU).

In recent years, GPUs dominated the high-performance computation field because of their

core counts reaching to thousands that lead to a very high processing throughput [10], [11]. The use of GPUs for general-purpose other than image processing is called General Purpose Computing on Graphical Processing Unit (GPGPU). The usage of GPGPUs for high performance has resulted in high speed gains in many applications. Computing on the graphics processor can provide significant performance improvements in parallel algorithms. The GPU and CPU together form a heterogeneous computing model. In this model, the programs take advantage of the powerful features of each unit.

Since the string matching is one of the classical computer science problems, it has also been studied on parallel systems for fast processing of string matching algorithms [14]. However, these studies tackle single algorithms and only aim to achieve higher performance against CPU for that specific algorithm. There is no comprehensive tool or code base for parallel string matching algorithms. For the serial implementation, the String Matching Algorithms Research Tool (SMART) provides an efficient and flexible tool designed for developing, testing, comparing, and evaluating 85 different string matching algorithms [15]. However, since the tool only provides a serial implementation of algorithms, not parallel, it is insufficient to meet the requirements of new systems, especially that requires high computation demands.

The direct transfer of serial methods is restrictive in achieving the actual performance of GPUs, and the solutions offered are application-specific. In this respect, string matching algorithms on GPGPU need to be redesigned and explored considering GPU architecture. Although the development of algorithms requires a certain amount of effort, we believe that the algorithms to be developed considering the limitations and possibilities of GPUs are much more efficient and promising than traditional methods and the best algorithms designed in serial architectures. In this thesis, we introduce CUSMART, which is a parallelization study on GPGPUs through the implementation of classical serial algorithms on GPUs with several optimization techniques applied.

The main contributions of this thesis can be listed as below:

- The parallelization of 85 string matching algorithms from the literature using the CUDA platform.

- Gathering these algorithms under one library called CUSMART in order to provide an easy to use testing environment.

- Optimization of these string matching algorithms to achieve good performance on parallel systems.

- Testing these parallel string matching algorithms on different scenarios to acquire a broad understanding of their behavior in several use cases.

- Determining the best and the worst performing algorithms in different scenarios to provide a guideline for different types of applications.

- Comparing desktop and mobile device performances for string matching operation.

This thesis is structured into chapters in the following order:

In chapter 2, background information required to explain the features of the CUSMART library is presented. This chapter includes brief explanations of the string matching algorithms present in our library and introductory knowledge about the CUDA architecture.

In chapter 3, related works from the literature are listed along with comparisons about their similarities and differences to our project.

In chapter 4, the implementation details of the CUSMART algorithm is presented. Features of the library and the considerations behind some design choices are also discussed in this chapter.

In chapter 5, we have discussed our experiment methodology, prepared test scenarios, and the results acquired by conducting these tests. The discussion about the test results is given in this chapter.

In chapter 6, we have presented our conclusion on the results of this work and shared our final thoughts for possible future works.

# 2. BACKGROUND

# 2.1. String Matching

String matching is the process of finding one or many occurrences of a string (which is generally called a *pattern*) in another string (generally called *text*)[16]. The pattern is defined as a finite array x = x [0..(m-1)] with  $m \ge 0$  where *m* is the length of pattern and the text is defined as a finite array y = y [0..(n-1)] with  $n \ge 0$  where *n* is the length of text. Both text and pattern are formed from a set of characters, which is called *alphabet* and represented as  $\Sigma$  with a length of  $\sigma$ .

Some additional definitions have to be introduced in order to continue the discussion on string matching [16]:

- A word *u* is called *prefix* of a word *w* if there is a word *v* (might be empty) that satisfies the condition *w* = *uv*.

- A word v is called *suffix* of a word w if there is a word u (might be empty) that satisfies the condition w = uv.

- A word *z* is called *substring* or *factor* or *subword* of word *w* if there are two words *u* and *v* that satisfies the condition *w* = *uzv*

String matching applications are divided into two types depending on the pattern and the text accessibility before the operation. Algorithms based on the access to pattern beforehand are called *online string matching algorithms*[16]. These algorithms aim to use the combinatorial properties of strings and automatons to preprocess the pattern and gain insight before the search. The other type of algorithms that have access to text before the searching operation aims to solve a problem called *offline string matching problem*. These algorithms use various techniques to index the text and try to gain knowledge to improve search performance before the operation. In this thesis, our focus will be on the online string matching algorithms.

There have been more than 120 online string matching algorithms proposed since 1970. These online string matching algorithms (we are going to refer them as string matching algorithms from now on) can be classified further under four different categories based on the primary strategy employed. These categories are comparison based algorithms, automata-based algorithms, bit-parallel algorithms, and packed algorithms. Some of the

algorithms listed under these categories follow a hybrid approach and use two or more of the methods listed above. For the sake of brevity, these algorithms are categorized under their most prominent category.

In the following sections, the algorithms included in our study will be listed in chronological order. Each algorithm entry will be given with a short description of their main features, and an acronym used to refer to this algorithm in the literature.

# 2.1.1. Comparison Based Algorithms

Algorithms using character comparison based strategies are the earliest examples of proposed string matching algorithms to the field. These algorithms process the pattern before the search operation to gain insight into its composition. This gained knowledge is often stored in auxiliary arrays called *shift tables*. When a mismatch occurs during the search operation, these tables are utilized to do improved shifts and prevent redundant character comparison operations.

When an algorithm is limited to sequential singular character reads of the text, the optimal complexity of this algorithm can be denoted as O(n). This was first demonstrated by the renowned Morris-Pratt algorithm [17]. However, often it is possible to complete the search operation without reading every character of the text, resulting in sublinear execution complexity on average. The optimal average time complexity for matching in a random string is given as  $O(n^{\log_{\sigma} m}/m)$  [18], and this is achieved by many algorithms. However, even the algorithms with a sub-linear average-case operation may need to read every character of the text in the worst-case scenario. Many of these algorithms have even worse O(nm) performance in the worst-case scenario [19], [20].

Although character comparison based strategy is not as dominant as it used to be in recent years, it still accounts for the majority of string matching algorithms proposed to this day. The character comparison algorithms related to our study are presented in the following section in chronological order.

# 2.1.1.1. Brute Force (BF) - N/A

Also known as the naive algorithm [21], the brute force algorithm is the most straightforward implementation of string matching. It checks every text character between 0 and n - m whether starts of a pattern is detected at the position or not. After each successful or failed attempt, a shift happens in the comparison window precisely by one step. The brute force algorithm does no preprocessing and requires constant extra space in memory. The comparison requires no specific order of operation and can be done in any order. The time complexity of the operation is O(nm) on the worst-case and O(n) at best. The algorithm makes 2n comparisons on average.

#### 2.1.1.2. Morris-Pratt (MP) - 1970

Morris-Pratt [17] is the first linear algorithm that emerged after an analysis of the bruteforce algorithm (2.1.1.1). The authors demonstrated that it is beneficial to remember the last matched part of the string after a mismatch and use this information to improve the length of the shifts. This improvement reduces comparisons needed and results in better performance. Morris-Pratt algorithm accomplishes this task by preprocessing the pattern and calculating the best shift length for every position in the pattern if a mismatch occurred at that position.

The preprocessing strategy is based on the fact that if a mismatch occurs at *i*th character of the pattern with 0 < i < m, there is no need to reprocess the text characters y[j..j+i] where *j* is the search window's position because we already acquired the information about these characters and know this substring is identical to our pattern, aside from the last, mismatched character. The time and space complexity of the preprocessing phase is O(m), and the time complexity of the searching phase is O(n + m). The searching phase time complexity is independent of  $\sigma$ .

# 2.1.1.3. Knuth-Morris-Pratt (KMP) - 1977

The Knuth-Morris-Pratt [22] algorithm is an improved version of Morris-Pratt algorithm (2.1.1.2). The preprocessing phase of this algorithm is improved to avoid another immediate mismatch after a shift, which resulted from a mismatch.

Aside from this improvement, space and time complexities of the algorithm are similar to MP, with O(m) preprocessing phase and O(n+m) search phase. The Knuth-Morris-Pratt algorithm performs 2n - 1 comparisons on the worst-case scenario.

# 2.1.1.4. Boyer-Moore (BM) - 1977

The Boyer-Moore [23] algorithm is another derivation of the brute-force algorithm (2.1.1.1), and it is considered as one of the most efficient string matching algorithms for practical applications. The simplified versions of this algorithm are often used as the search function in text processors [24].

The algorithm applies the left-to-right comparison idea along with a sliding search window approach to achieve the sub-linear time complexity of O(n/m) for the best-case searching scenario. This value remains as the best lower bound achieved for string matching to date. Aside from the left-to-right comparison scan order, the Boyer-Moore algorithm also uses multiple rules such as "bad character rule" and "good suffix rule" to generate shift tables and evaluate these tables when a mismatch occurs in order to determine the longest shift possible. The time and space complexity of the preprocessing phase is  $O(m + \sigma)$ . In the worst-case scenario, the algorithm does 3n comparisons when searching for a non-periodic pattern.

#### 2.1.1.5. Horspool (HOR) - 1980

The Horspool algorithm [25] is a simplification of the Boyer-Moore algorithm 2.1.1.4. This algorithm only uses the "bad character rule" table of the Boyer-Moore for the rightmost character of the search window, which improves the average search performance on large alphabets like ASCII. The preprocessing phase is in  $O(m + \sigma)$  time and has  $O(\sigma)$  space complexity.

# 2.1.1.6. Galil-Seiferas (GS) - 1981

The Galil-Seiferas algorithm [26] is a linear algorithm using constant extra space for its auxiliary data structure. The preprocessing step employs a decomposition strategy called *perfect factorization*. The algorithm has O(m) preprocessing phase time complexity and makes 5n comparisons in the worst-case scenario.

#### 2.1.1.7. Apostolico-Giancarlo (AG) - 1986

The Apostolico-Giancarlo algorithm [27] is another variant of The Boyer-Moore algorithm (2.1.1.4). This algorithm stores some of the information that is extracted from the text by the Boyer-Moore algorithm but then forgotten after the comparison is made. Using this stored information, the Apostolico-Giancarlo algorithm reduces the worst-case comparison amount to half, which is 3/2n.

## 2.1.1.8. Karp-Rabin (KR) - 1987

The Karp-Rabin [28] is the first string matching algorithm that used a hashing function in the comparison step. The algorithm compares the hash of search window and pattern hash first to test the pattern on a given window quickly. If a similarity is detected, the algorithm compares the remaining characters regularly. Unloading the first check to hash control avoids a quadratic number of character comparisons in most practical situations. The algorithms preprocessing phase time complexity is O(m) with constant space, and the expected running complexity is O(n + m).

#### 2.1.1.9. Zhu-Takaoka (ZT) - 1987

The Zhu-Takaoka algorithm [29] is a variant of the Boyer-Moore algorithm (2.1.1.4), which performs the bad character shift based on the last two characters of the search window instead of one. This change caused an improved average-case performance at the cost of  $O(m + \sigma^2)$  preprocessing phase time complexity.

# 2.1.1.10. Quick Search (QS) - 1990

The Quick Search algorithm [30] is a simplified version of the Boyer-Moore algorithm (2.1.1.4), which uses only the bad character shift table like the Horspool algorithm (2.1.1.5). Their version is shorter, easy to implement, and pretty fast in practice for short patterns on large alphabets.

# 2.1.1.11. Optimal Mismatch (OM) - 1990

The Optimal Mismatch algorithm [30] is a variation of the Quick Search algorithm (2.1.1.10), and uses the character frequencies in a given alphabet. The algorithm compares the characters of the pattern in a custom order from less frequent to more frequent to "optimize mismatch". Like in the Boyer-Moore algorithm, early mismatches provide long shifts that allow the algorithm to scan the text quicker.

# 2.1.1.12. Maximal Shift (MS) - 1990

The Maximal Shift algorithm [30] is a variation of the Quick Search algorithm (2.1.1.10), that uses a custom scan order prioritizing the comparisons that result in long shifts. The preprocessing phase has  $O(m^2 + \sigma)$  time and  $O(m + \sigma)$  space complexity.

# 2.1.1.13. Apostolico-Crochemore (AC) - 1991

The Apostolico-Crochemore algorithm [31] is an improved version of the Knuth-Morris-Pratt algorithm (2.1.1.3). This algorithm reduces the worst-case comparison amount to  $^{3}/_{2n}$  from 2n - 1 of the Knuth-Morris-Pratt.

### 2.1.1.14. Two Way (TW) - 1991

The Two Way algorithm [32] factorizes the pattern into two parts and does the comparison steps from center to borders. The left part is scanned from right to left while the right part is scanned from left to right. The algorithm has a linear running time of O(2n - m) on worst-case and runs in O(n) on average. The algorithms preprocessing phase time complexity is O(m) with constant space.

#### 2.1.1.15. Tuned Boyer-Moore (TUNBM) - 1991

The Tuned Boyer-Moore algorithm [33] is an improved version of the Boyer-Moore algorithm (2.1.1.4). This algorithm adds a fast path that unrolls a certain number of early comparisons and makes a few blind shifts without comparing the pattern characters other than the last one. This approach speeds up the algorithm in practice with the introduction of the fast path.

## 2.1.1.16. Colussi (COL) - 1991

The Colussi algorithm [34] is a refinement of the Knuth-Morris-Pratt algorithm, which uses a factorized pattern similar to the Two Way algorithm (2.1.1.14) and improves the worst-case performance to 3/2n maximum comparisons. The time and space complexity of the preprocessing phase is O(m).

# 2.1.1.17. Smith (SMITH) - 1990

The Smith algorithm [35] combines the approaches of the Horspool algorithm (2.1.1.5) with The Quick Search algorithm (2.1.1.10). The algorithm compares the bad character shift function results of these two algorithms and selects the more significant value for a longer shift.

## 2.1.1.18. Galil-Giancarlo (GG) - 1992

The Galil-Giancarlo algorithm [36] is an improved version of the Colussi algorithm (2.1.1.16) which reduces the worst-case comparison amount to  $\frac{4}{3n}$ .

## 2.1.1.19. Raita (RAITA) - 1992

The Raita algorithm [37] is a modified version of the Horspool algorithm (2.1.1.5) that uses a different scan order. The algorithm compares the last character then the first character; if both comparisons are matches, then it proceeds to compare the rest of the pattern.

# 2.1.1.20. String Matching on Ordered Alphabet (SMOA) - 1992

The String Matching on Ordered Alphabet algorithm [38] uses constant extra space and has no preprocessing phase. The algorithm makes 6n + 5 comparisons at worst.

#### 2.1.1.21. Turbo Boyer-Moore (TBM) - 1992

The Turbo Boyer-Moore algorithm [39] is an improved version of the Boyer-Moore algorithm (2.1.1.4). The algorithm lowers the maximum required comparison amount to 2n by remembering the last matched suffix and altering the decision mechanism slightly. This version requires no extra preprocessing and only constant extra space.

# 2.1.1.22. Not So Naive (NSN) - 1993

The Not So Naive algorithm [40] is a simple algorithm that is similar to the Brute Force algorithm (2.1.1.1). This algorithm's comparison order starts from the second character and goes until the end; then, it compares the first character as the last step. This approach allows two-character shifts instead of one when the first comparison results in a mismatch and improves the average-case complexity to slightly sub-linear.

#### 2.1.1.23. Reverse Colussi (RCOL) - 1994

The Reverse Colussi algorithm [41] is a combination of the Colussi algorithm (2.1.1.16) and the Boyer-Moore algorithm (2.1.1.4). By employing the Colussi algorithm's factorization scheme on the Boyer-Moore style search, this algorithm lowers the worst-case maximum comparison amount to 2n. The preprocessing phase has  $O(m^2)$  time and  $O(m\sigma)$  space complexity.

#### 2.1.1.24. Skip Search (SKIP) - 1998

The Skip Search algorithm [42] processes each character in the pattern and builds a data structure called "buckets of positions". This structure holds the shift amounts for every character in the pattern and has the width of alphabet size  $\sigma$ . After a right-to-left ordered comparison, the algorithm determines a proper shift via these buckets of positions, then proceeds to compare the rest of the string in a left-to-right fashion.

#### 2.1.1.25. Alpha Skip Search (ASKIP) - 1998

The Alpha Skip Search algorithm [42] is an improved version of the Skip Search algorithm (2.1.1.24). This version uses a bucket of positions for each factor of the pattern instead of character.

# 2.1.1.26. Knuth-Morris-Pratt Skip Search (KMPS) - 1998

The Knuth-Morris-Pratt Skip Search algorithm [42] is another variant of the Skip Search algorithm (2.1.1.24). This variant uses the shift tables of the Knuth-Morris-Pratt algorithm (2.1.1.3).

# 2.1.1.27. Berry-Ravindran (BR) - 1999

The Berry-Ravindran algorithm [43] is a hybrid between Zhu-Thakaoka (2.1.1.9) and Quick Search (2.1.1.10) algorithms. The algorithm is designed to do two consecutive shifts based on the bad-character shift table. It has  $O(m + \sigma^2)$  space and time complexity.

# 2.1.1.28. Ahmed-Kaykobad-Chowdhury (AKC) - 2003

The Ahmed-Kaykobad-Chowdhury algorithm [44] is a variant of the Apostolico-Giancarlo algorithm (2.1.1.7). This algorithm remembers the pattern suffixes found in the text and alters the shifts accordingly.

#### 2.1.1.29. Fast Search (FS) - 2003

The Fast Search algorithm [45] presents another improvement to the Boyer-Moore algorithm (2.1.1.4) by employing some occurrence heuristics for the first mismatch case.

# 2.1.1.30. Forward Fast Search (FFS) - 2004

The Forward Fast Search algorithm [45] combines the Fast Search algorithm (2.1.1.29) with the Quick Search algorithm and implements good-suffix heuristics using the following character's information on the current search window of text.

#### 2.1.1.31. Backwards Fast Search (BFS) - 2004

The Backwards Fast Search algorithm [45] is a combination of the Boyer-Moore algorithm (2.1.1.4) and the Horspool algorithm (2.1.1.5). It implements good-suffix heuristics using the mismatching character information.

# 2.1.1.32. Tailed Substring (TS) - 2004

The Tailed Substring algorithm [46] employs a variation of occurrence heuristics used in the Horspool algorithm (2.1.1.5) to improve the naive approach.

## 2.1.1.33. Sheik-Sumit-Anindya-Balakrishnan-Sekar (SSABS) - 2004

The Sheik-Sumit-Anindya-Balakrishnan-Sekar algorithm [47] uses the concepts found in the Raita algorithm (2.1.1.19) and the Quick Search algorithm (2.1.1.10).

# 2.1.1.34. Thathoo-Virmani-Sai-Balakrishan-Sekar (TVSBS) - 2006

The Thathoo-Virmani-Sai-Balakrishan-Sekar algorithm [47] combines the SSABS algorithm (2.1.1.33) and the Berry-Ravindran algorithm (2.1.1.27).

# 2.1.1.35. Boyer-Moore-Horspool using Probabilities (PBMH) - 2006

The Boyer-Moore-Horspool using Probabilities algorithm [47] applies the statistical character analysis approach of the Optimal Mismatch algorithm (2.1.1.11) to the Horspool algorithm (2.1.1.5).

# 2.1.1.36. Franek-Jennings-Smyth (FJS) - 2007

The Franck-Jennings-Smyth algorithm [48] applies the concepts found in the Quick Search algorithm (2.1.1.10) to the Knuth-Morris-Pratt algorithm (2.1.1.3).

# 2.1.1.37. Wu-Manber for Single Pattern Matching (HASHQ) - 2007

The Wu-Manber for Single Pattern Matching algorithm [49] is an improvement over the Horspool algorithm (2.1.1.5). This algorithm demonstrates a use case of super alphabets and computes the q-gram fingerprints of the pattern using a hashing function.

## 2.1.1.38. Boyer-Moore-Horspool with q-grams (BMHQ) - 2008

The Boyer-Moore-Horspool with q-grams algorithm [50] offers a new approach to the well-known Horspool algorithm (2.1.1.5). The algorithm introduces the use of q-grams to compute the occurrence heuristics.

# 2.1.1.39. Two Sliding Windows (TSW) - 2008

The Two Sliding Windows algorithm [50] is an improvement of the Quick Search algorithm (2.1.1.10) that adds another search window to the process. The first window processes from left to right while the second window processes from right to left.

#### 2.1.2. Automata based algorithms

The automata based algorithms are indispensable tools in the field of string matching as they are able to handle the string matching tasks very efficiently. The first algorithm applying the technique to string matching, Deterministic Finite Automata was one of the first algorithms that achieved linear time complexity on the search task [21]. Then there is the Backward DAWG Matching algorithm, which reached the optimal lower bound  $O(n \log_{\sigma}(m)/m)$  time complexity for the average case. Both these algorithms capitalize on the advantages of using a finite automaton for the job. The efficiency of a given algorithm is varied based on the automaton used for pattern representation and the simulation technique of automata if it is present.

Most of the algorithms in this section stem from the Deterministic Finite Automata (2.1.2.1) and apply the concepts found in comparison based algorithms (2.1.1) to automata-based string matching.

The following list contains the automata-based string matching algorithms that are relevant to our study in chronological order.

# 2.1.2.1. Deterministic Finite Automata (DFA) - N/A

The Deterministic Finite Automata [21] is a string matching algorithm that works in linear time. In order to perform the search, the algorithm first builds a Deterministic String Automaton A(x) from the pattern x. The preprocessing phase which consist of the construction of automaton has  $O(m + \sigma)$  time and  $O(m\sigma)$  space complexity. After the Deterministic Finite Automaton is constructed, searching of the pattern for a given text y can be accomplished by parsing the text character by character using the automaton A(x) and advancing the state each time a termination occurs. If the automaton structure is stored in a direct access table, the search step can be completed in O(n) time. Else, it takes  $O(n \log \sigma)$  time to complete the search.

# 2.1.2.2. Reverse Factor (RF) - 1992

The Reverse Factor algorithm [51] applies the Boyer-Moore algorithm (2.1.1.4) strategies to the Deterministic Finite Automata (2.1.2.1). The algorithm builds a suffix automaton from the reversed version of the pattern. The time complexity of the worst-case search operation is O(mn).

# 2.1.2.3. Simon (SIM) - 1994

The Simon algorithm [52] is a modification of the Deterministic Finite Automata (2.1.2.1). The algorithm builds a minimal automaton by processing the pattern.

## 2.1.2.4. Turbo Reverse Factor (TRF) - 1994

The Turbo Reverse Factor algorithm [53] improves over the Reverse Factor algorithm (2.1.2.2). The algorithm remembers the last matched prefix of the pattern to avoid redundant comparison operations. By utilizing this strategy, it is possible to achieve O(2n) worst-case time complexity.

### 2.1.2.5. Forward DAWG Matching (FDM) - 1994

The Forward DAWG Matching algorithm [53] uses a smallest suffix automaton (also called Directed Acyclic Word Graph) to achieve linear time search operation. This was a notable algorithm among string matching algorithms of its era because of its constant search operation time, which is not affected by the length of the pattern. The algorithm has O(n) time complexity and performs exactly *n* comparisons even on the worst-case.

# 2.1.2.6. Backward DAWG Matching (BDM) - 1994

The Backward DAWG Matching algorithm [53] is a variant of the Reverse Factor algorithm (2.1.2.2) and uses Directed Acyclic Word Graph of the pattern. The algorithm works similarly to the Forward DAWG Matching algorithm (2.1.2.5), but the scan direction is reversed to right-to-left.

# 2.1.2.7. Backward Oracle Matching (BOM) - 1999

The Backward Oracle Matching algorithm [54] is a variation of the Reverse Factor algorithm (2.1.2.2) that uses the suffix oracle of the pattern instead of the suffix automaton. The suffix oracle data structure is a very compact automaton with the capability of recognizing at least all suffixes of a word. Although the suffix oracle also recognizes the factors not present in the pattern, it still can be used for string search because the only factor recognized by the oracle that has a length of m or longer is the pattern itself in its reversed form. The time and space required for the preprocessing phase are O(m). The algorithm achieves optimal time in average-case and has O(mn) worst-case complexity.

#### 2.1.2.8. Double Forward DAWG Matching (DFDM) - 2000

The Double Forward DAWG Matching algorithm [55] is a modification of the Forward DAWG Matching algorithm (2.1.2.5). The algorithm achieves linear worst-case time by using another DAWG that is constructed from the reverse of the pattern.

## 2.1.2.9. Wide Window (WW) - 2005

The Wide Window algorithm [56] is a combination of the Reverse Factor algorithm (2.1.2.2) and the Forward DAWG Matching algorithm (2.1.2.5). By employing two automata built from the suffixes of pattern and the prefixes of the reverse of the pattern, this algorithm achieves linear time in the worst-case scenario.

# 2.1.2.10. Linear DAWG Matching (LDM) - 2005

The Linear DAWG Matching algorithm [56] combines the automata from the Deterministic Finite Automata (2.1.2.1) and the Backward DAWG Matching algorithm (2.1.2.6). Deterministic finite automaton of the pattern is utilized along with the suffix automaton of the pattern.

#### 2.1.2.11. Improved Linear DAWG Matching (ILDM) - 2006

The Improved Linear DAWG Matching algorithm [57] applies some tweaks over the Linear DAWG Matching algorithm (2.1.2.10). There are two versions of this algorithm referenced as ILDM1 and ILDM2, which are published in the same study.

#### 2.1.2.12. Extended Backward Oracle Matching (EBOM) - 2008

The Extended Backward Oracle Matching algorithm [58] is an improved version of the Backward Oracle Matching algorithm (2.1.2.7). The algorithm performs transitions based on the checks of two characters instead of one.

# 2.1.2.13. Forward Backward Oracle Matching (FBOM) - 2008

The Forward Backward Oracle Matching algorithm [58] applies the Quick Search algorithm (2.1.1.10) strategies to the Extended Backward Oracle Matching algorithm (2.1.2.12). The transitions are performed based on the characters trailing the current search window.

# 2.1.2.14. Simplified Extended Backward Oracle Matching (SEBOM) - 2009

The Simplified Extended Backward Oracle Matching algorithm [59] is a simplified version of the Extended Backward Oracle Matching algorithm (2.1.2.12).

## 2.1.2.15. Simplified Forward Backward Oracle Matching (SFBOM) - 2009

The Simplified Forward Backward Oracle Matching algorithm [59] is a simplified version of the Forward Backward Oracle Matching algorithm (2.1.2.13).

## 2.1.2.16. Backward SNR DAWG Matching (BSDM) - 2012

The Backward SNR DAWG Matching algorithm [60] is a modified version of the Backward DAWG Matching algorithm (2.1.2.6). The DAWG structure used on this algorithm is built from the longest substring of the pattern that contains no repeated characters.

#### 2.1.3. Bit-Parallel Based Algorithms

Bit-parallelism is a technique based on the efficient simulation of nondeterministic automata [20]. It takes advantage of the computing unit's inherent properties, in which bit-wise operations can be performed word by word in parallel. This parallelism can be used to cut down the number of instructions required for comparisons in the search step. The number of operations required can be cut down by a factor of w, where w is the number of bits contained in the word that the processor can handle. This property makes bit-parallel algorithms considerably fast when the pattern length  $m \le w$  so that the pattern can fit into a computer word, and only a single operation is sufficient for parallel comparison. The performance of bit-parallel algorithms starts to degrade considerably once the m > w, as the m/w grows.

The following list contains the bit-parallelism based string matching algorithms that are relevant to our study in chronological order.

# 2.1.3.1. Shift-Or (SO) - 1989

The Shift-Or algorithm [61] is the first bit-parallelism technique applied to the string matching problem. The algorithm uses bitwise OR operation followed by shift operations to scan the text for the occurrence of a given pattern. The efficiency of the algorithm is high when the pattern fits into a single computer word. The complexity of this algorithm is O(n) for all scenarios, and running time is not affected by the pattern length or the alphabet size. The preprocessing phase takes  $O(m + \sigma)$  time and requires  $O(m + \sigma)$  space. This algorithm is suitable for approximate string matching operations with minor tweaks.

## 2.1.3.2. Shift-And (SA) - 1989

The Shift-And algorithm [61] is similar to the Shift-Or algorithm (2.1.3.1) and simulates a nondeterministic version of the Deterministic Finite Automata algorithm (2.1.2.1). Unlike the Shift-Or algorithm, this algorithm uses bitwise AND operation as the comparison method.

# 2.1.3.3. Backward Nondeterministic DAWG Matching (BNDM) - 1998

The Backward Nondeterministic DAWG Matching algorithm [62] is a nondeterministic simulation of the Backward DAWG Matching algorithm (2.1.2.6).

# **2.1.3.4.** Backward Nondeterministic DAWG Matching for Long Patterns (LBNDM) - 2000

The Backward Nondeterministic DAWG Matching for Long Patterns algorithm [63] improves the behavior of the BNDM algorithm (2.1.3.3) over long patterns.

# 2.1.3.5. Simplified Backward Nondeterministic DAWG Matching (SBNDM) - 2003

The Simplified Backward Nondeterministic DAWG Matching algorithm [64] is an improved version of the Backward Nondeterministic DAWG Matching algorithm (2.1.3.3).

# 2.1.3.6. Two-Way Nondeterministic DAWG Matching (TNDM) - 2003

The Two-Way Nondeterministic DAWG Matching algorithm [64] is a variation of the Backward Nondeterministic DAWG Matching algorithm (2.1.3.3). The algorithm performs a forward scan of the pattern suffix before the backward scan.

# 2.1.3.7. Shift Vector Matching (SVM) - 2003

The Shift Vector Matching algorithm [64] implements a variation of the Boyer-Moore algorithm (2.1.1.4) using bit-parallelism. The information gathered during the last comparison attempt is stored to improve the performance.

# 2.1.3.8. BNDM with loop unrolling (BNDM2) - 2005

The BNDM with loop unrolling algorithm [65] improves the performance of the Backward Nondeterministic DAWG Matching algorithm (2.1.3.3) via unrolled loops and blind shifts.

# 2.1.3.9. Simplified BNDM with loop unrolling (SBNDM2) - 2005

The Simplified BNDM with loop unrolling algorithm [65] improves the performance of the Simplified Backward Nondeterministic DAWG Matching via loop unrolling method.

# 2.1.3.10. BNDM with Boyer-Moore-Horspool Shift (BNDMBMH) - 2005

The BNDM with Boyer-Moore-Horspool Shift algorithm [65] combines the Backward Nondeterministic DAWG Matching algorithm (2.1.3.3) with the shift tables from the Horspool algorithm (2.1.1.5).

# 2.1.3.11. Horspool with BNDM test (BMHBNDM) - 2005

The Horspool with BNDM test algorithm [65] is another approach at combining the Horspool algorithm (2.1.1.5) with the BNDM algorithm (2.1.3.3).

# 2.1.3.12. Forward Nondeterministic DAWG Matching (FNDM) - 2005

The Forward Nondeterministic DAWG Matching algorithm [65] is a simulated nondeterministic version of the Forward DAWG Matching (2.1.2.5).

# 2.1.3.13. Bit Parallel Wide Window (BWW) - 2005

The Bit Parallel Wide Window algorithm [56] is a simulated nondeterministic version of the Wide Window algorithm (2.1.2.9).

# 2.1.3.14. Average Optimal Shift-Or (AOSO) - 2005

The Average Optimal Shift-Or algorithm [66] borrows the optimal shift concept from the Optimal Shift algorithm (2.1.1.11) and applies to the Shift-Or algorithm (2.1.3.1). This modification allows longer shifts and improves performance.

# 2.1.3.15. Fast Average Optimal Shift-Or (FAOSO) - 2005

The Fast Average Optimal Shift-Or algorithm [66] is an improved version of the Average Optimal Shift-Or algorithm (2.1.3.14).

# 2.1.3.16. Forward BNDM (FBNDM) - 2008

The Forward BNDM algorithm [58] is a simulated nondeterministic version of the Forward Backward Oracle Matching algorithm (2.1.2.13).

# 2.1.3.17. Forward Simplified BNDM (FSBNDM) - 2008

The Forward Simplified BNDM algorithm [58] is a combination of the Simplified BNDM algorithm (2.1.3.5) and the Forward BNDM algorithm (2.1.3.16).

# 2.1.3.18. Bit-Parallel Length Invariant Matcher (BLIM) - 2008

The Bit-Parallel Length Invariant Matcher algorithm [67] tries to overcome the pattern length limitation of the bit-parallel algorithms like the Backward Nondeterministic DAWG Matching (2.1.3.3) with a length invariant approach. The algorithm shows improved performance over small alphabet searches like DNA matching.

# 2.1.3.19. Backwards Nondeterministic DAWG Matching with q-grams (BNDMQ) - 2009

The Backwards Nondeterministic DAWG Matching with q-grams algorithm [68] is another BNDM algorithm (2.1.3.3) variant that uses super alphabets approach implemented via q-grams.

# 2.1.3.20. Simplified BNDM with q-grams (SBNDMQ) - 2009

The Simplified BNDM with q-grams algorithm [68] is a variant of the SBNDM algorithm (2.1.3.5) employing q-gram based super alphabets.

# 2.1.3.21. Forward Nondeterministic DAWG Matching with q-grams (FNDMQ) - 2009

The Forward Nondeterministic DAWG Matching with q-grams algorithm [68] is an implementation of the Forward Nondeterministic DAWG Matching algorithm (2.1.3.12) using q-grams.

# 2.1.3.22. Small Alphabet Bit-Parallel (SABP) - 2009

The Small Alphabet Bit-Parallel algorithm [69] is designed to work on small alphabets like binary and DNA. It uses a match table built based on the character positions.

# **2.1.3.23.** Backwards Nondeterministic DAWG Matching with Extended shifts (BXS) - 2010

The Backwards Nondeterministic DAWG Matching with Extended shifts algorithm [70] is an optimized version of the Backwards Nondeterministic DAWG Matching algorithm (2.1.3.3) for long patterns. The algorithm uses a higher level pattern layered over the pattern to construct the automata of long patterns.

# 2.1.3.24. Factorized BNDM (KBNDM) - 2010

The Factorized BNDM algorithm [71] is a simulated nondeterministic version of the Backward Nondeterministic DAWG Matching algorithm (2.1.3.3). The algorithm builds a brief version of the automaton based on the pattern factorization.

## 2.2. General-purpose Computing on Graphics Processing Unit with CUDA

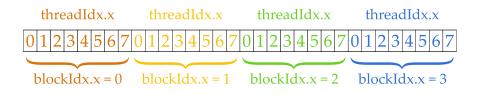

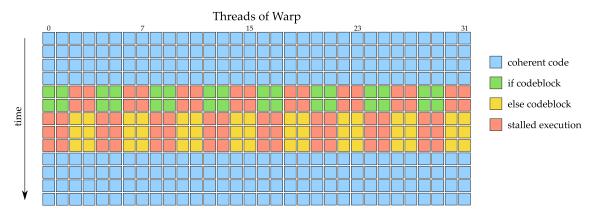

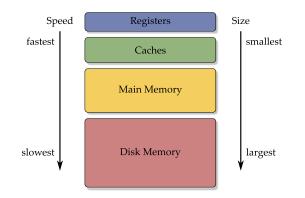

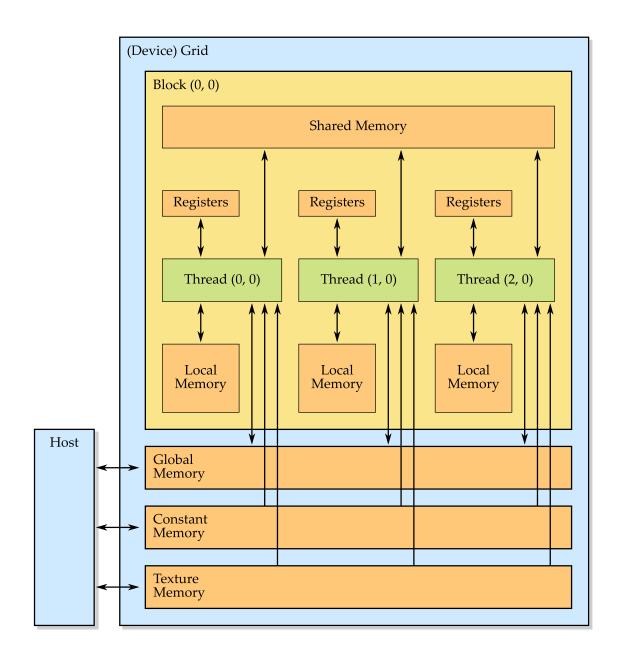

The High-Performance Computing (HPC) environment is continually evolving as new technology and methods become widespread, and HPC concept shifts accordingly. Generally, it involves the use of multiple processors or computers to perform a complex task in parallel in order to achieve high throughput in an efficient manner [72]. High-performance computing has developed dramatically over the last decade, mainly thanks to the emergence of heterogeneous architectures using GPU-CPU pair, which has led to a fundamental shift in parallel programming.